Quartusでのpost-synthesis simulationの方法(GUI編)

QuartusのGUIモードでのpost-synthesis simulationの方法を紹介します。

ここで記載している手順は、基本的にここに載っています。

Quartus® Prime Standard Edition Handbook Volume 3: Verification

https://www.altera.com/en_US/pdfs/literature/hb/qts/qts-qps-5v3.pdf

事前インストール

下記の事前インストールが必要です。

- Quartus Prime (Lite EditionでOK)

- なんらかのデバイスファイル (e.g. MAX 10)

- Modelsim-Altera (Starter EditionでOK)

デザインとテストベンチ

ここでは実験用として以下のファイルを用意します。counterディレクトリに置きます。

- counter.v

module counter( input clk, input rst_n, output reg [3:0] count ); always@( posedge clk ) if( !rst_n ) count <= 4'd0; else count <= count + 4'd1; endmodule

- test_counter.v

`timescale 1ns/1ps module test_counter; reg clk; reg rst_n; wire [3:0] count; initial begin forever begin clk = 1; #5; clk = 0; #5; end end initial begin rst_n = 0; #16; rst_n = 1; @( posedge clk ); $display( "cycle #0 %d %s", count, (count == 4'd0) ? "OK" : "NG" ); @( posedge clk ); $display( "cycle #1 %d %s", count, (count == 4'd1) ? "OK" : "NG" ); @( posedge clk ); $display( "cycle #2 %d %s", count, (count == 4'd2) ? "OK" : "NG" ); @( posedge clk ); $display( "cycle #3 %d %s", count, (count == 4'd3) ? "OK" : "NG" ); @( posedge clk ); $display( "cycle #4 %d %s", count, (count == 4'd4) ? "OK" : "NG" ); @( posedge clk ); $display( "cycle #5 %d %s", count, (count == 4'd5) ? "OK" : "NG" ); $finish; end counter dut( .clk(clk), .rst_n(rst_n), .count(count) ); endmodule

手順

プロジェクト作成

Quartusを起動し、File->New...->New Quartus Prime Project

Nextをクリック

counter.v, test_counter.vのある場所を指定する。Nextをクリック

Nextをクリック

Nextをクリック

適当にデバイスを選択する。Nextをクリック

SimulationでModelsim-Alteraを選択する。Finishをクリック

下準備

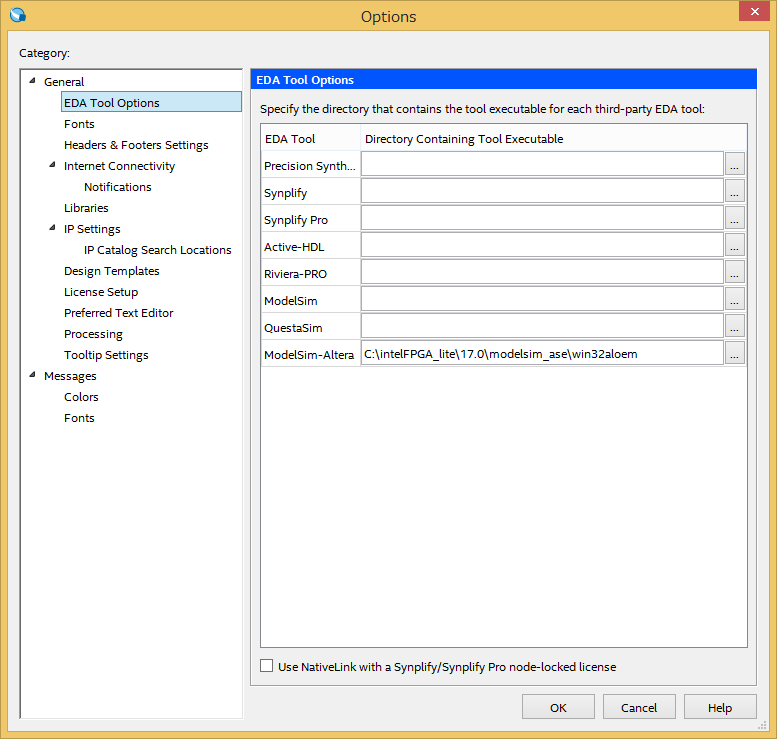

- Tool->Options->General->EDA Tool OptionsでModelsim-Alteraのインストール場所を指定する

- Project->Add/Remove Files in Projectでcounter.vを追加

- 同ウィンドウ、EDA Tool Settings->Simulation->NativeLink settings で Compile testbench: を選択し、Test Benches...をクリック

- New...をクリック。test_counter.vを追加する。OKをクリック。

- Post-Synthesis Simulationで機能検証のみ行いたい(遅延モデル無しのシミュレーションをしたい)場合、同画面「More EDA Netlist Writer Settings...」でGenerate functional simulation netlistをOnにする

合成

- EDA Netlist Writerをダブルクリック

Modelsimの起動

- Tools->Run Simulation Tools->Gate Level Simulation...をクリック

自動的にシミュレーションが走る。